線路side by side布局時,最擔心的就是邊緣耦合干擾到線路特性,其中以遠端耦合(FEXT)造成的影響最為可怕,因為從串音干擾(3):近端耦合與遠端耦合一文裡我們知道FEXT有著時間較短能量較強的特性,容易一次大量的干擾訊號,使的接收晶片眼圖更差,更容易產生誤判斷。

要最有效率地降低FEXT的方法就是將走線布局在內層,也就是帶狀線(Stripline)。

在帶狀線中,由於板子上下是對稱性結構,而且材料一致,所以奇模與偶模不會有場型差異,這將使得奇模速度與偶模速度一致!

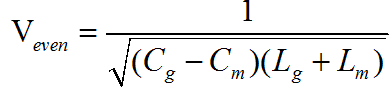

我們可以用數學公式來看待:

因為

所以可以得到結論是

大家有沒有覺得這式子很眼熟?似曾相識的感覺,我們將文章切換到串音干擾(4) :如何降低耦合雜訊CROSSTALK,FEXT的數學公式為

這樣就一目瞭然了,帶狀線的FEXT在數學上的確為0,不過這當然是屬於理想的帶狀線才會有的結果,現實上板子的厚度與材料的DK值不太可能做到上下層完全一樣,因此不可能完全沒有FEXT,但是已經是現有做法裡最有效抑制FEXT的方法了!(除非你想把線距拉的很開)

同步更新: